CMOS集成電路設(shè)計(jì)中的邏輯門電路分析

在當(dāng)今的數(shù)字電子世界中,互補(bǔ)金屬氧化物半導(dǎo)體(CMOS)技術(shù)是超大規(guī)模集成電路(VLSI)的基石。其核心構(gòu)件——CMOS邏輯門電路,以其低功耗、高噪聲容限和優(yōu)異的可擴(kuò)展性,主導(dǎo)著從微處理器到存儲芯片的幾乎所有數(shù)字系統(tǒng)設(shè)計(jì)。深入分析CMOS邏輯門的工作原理、特性及設(shè)計(jì)考量,是掌握集成電路設(shè)計(jì)的關(guān)鍵。

一、CMOS邏輯門的基本結(jié)構(gòu)與工作原理

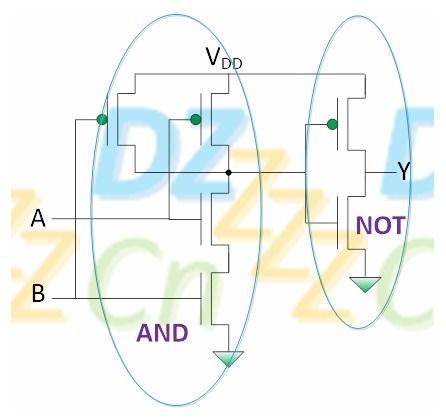

CMOS邏輯門的基本結(jié)構(gòu)由兩種類型的MOSFET(金屬氧化物半導(dǎo)體場效應(yīng)晶體管)構(gòu)成:P溝道MOSFET(PMOS)和N溝道MOSFET(NMOS)。這兩種晶體管以互補(bǔ)的方式連接。其核心工作原理在于:對于任何給定的輸入組合,PMOS網(wǎng)絡(luò)和NMOS網(wǎng)絡(luò)中總有一個(gè)處于截止(關(guān)斷)狀態(tài),從而在穩(wěn)態(tài)下,從電源(VDD)到地(GND)之間沒有直接的直流電流通路。這是CMOS電路靜態(tài)功耗極低的根本原因。

以最基本的CMOS反相器(非門)為例:一個(gè)PMOS管連接在電源和輸出端之間,一個(gè)NMOS管連接在輸出端和地之間。當(dāng)輸入為高電平時(shí),NMOS導(dǎo)通,PMOS截止,輸出被下拉至低電平;當(dāng)輸入為低電平時(shí),PMOS導(dǎo)通,NMOS截止,輸出被上拉至高電平。這種推挽式輸出結(jié)構(gòu)提供了對負(fù)載電容的快速充放電能力。

二、復(fù)合邏輯門的設(shè)計(jì):與非門(NAND)和或非門(NOR)

通過將多個(gè)PMOS和NMOS晶體管以特定方式組合,可以構(gòu)建更復(fù)雜的邏輯功能。設(shè)計(jì)遵循以下規(guī)則:

- NMOS網(wǎng)絡(luò):實(shí)現(xiàn)邏輯函數(shù)的“下拉”路徑,串聯(lián)實(shí)現(xiàn)“與”操作,并聯(lián)實(shí)現(xiàn)“或”操作。

- PMOS網(wǎng)絡(luò):實(shí)現(xiàn)邏輯函數(shù)的“上拉”路徑,是NMOS網(wǎng)絡(luò)的對偶,即串聯(lián)對應(yīng)“或”,并聯(lián)對應(yīng)“與”。

例如,一個(gè)二輸入CMOS與非門由兩個(gè)串聯(lián)的NMOS管(下拉網(wǎng)絡(luò))和兩個(gè)并聯(lián)的PMOS管(上拉網(wǎng)絡(luò))構(gòu)成。只有當(dāng)兩個(gè)輸入均為高時(shí),兩個(gè)NMOS才都導(dǎo)通,將輸出拉低;只要有一個(gè)輸入為低,對應(yīng)的PMOS就會導(dǎo)通,將輸出拉高,完美實(shí)現(xiàn)了“與非”功能。

三、關(guān)鍵性能參數(shù)分析

在集成電路設(shè)計(jì)中,對邏輯門的分析遠(yuǎn)不止于邏輯功能,更關(guān)注其電氣性能:

- 電壓傳輸特性(VTC):描述了輸出電壓隨輸入電壓變化的曲線。關(guān)鍵指標(biāo)包括邏輯擺幅(通常接近VDD和GND)、噪聲容限(高電平噪聲容限和低電平噪聲容限)以及開關(guān)閾值(VTC曲線中Vin=Vout的點(diǎn))。

- 傳播延遲:信號從輸入變化到引起輸出變化所需的時(shí)間,通常定義為輸入輸出波形50%點(diǎn)之間的時(shí)間差。它受晶體管尺寸、負(fù)載電容和電源電壓的顯著影響。

- 功耗:

- 動態(tài)功耗:主要由對負(fù)載電容充放電的開關(guān)功耗構(gòu)成(∝ CL * VDD^2 * f),是CMOS電路功耗的主要來源。

- 靜態(tài)功耗:在理想穩(wěn)態(tài)下應(yīng)接近于零,但實(shí)際上由于亞閾值漏電流等因素,深亞微米工藝下靜態(tài)功耗已變得不可忽視。

- 扇入與扇出:扇入指門的輸入數(shù)量,增加扇入會因晶體管串聯(lián)而增加延遲。扇出指門能驅(qū)動的同類門輸入數(shù)量,增加扇出會增加負(fù)載電容,同樣導(dǎo)致延遲增加。

四、集成電路設(shè)計(jì)中的優(yōu)化與折衷

在實(shí)際的CMOS集成電路設(shè)計(jì)中,邏輯門分析是性能、面積和功耗之間精細(xì)平衡的起點(diǎn):

- 晶體管尺寸調(diào)整:通過調(diào)整PMOS和NMOS的溝道寬度(W),可以優(yōu)化延遲、噪聲容限和驅(qū)動能力。通常,為了使上升時(shí)間和下降時(shí)間對稱,PMOS管的寬度被設(shè)計(jì)為NMOS管的2至3倍(因?yàn)榭昭ㄟw移率低于電子遷移率)。

- 工藝縮放的影響:隨著工藝節(jié)點(diǎn)不斷縮小,電源電壓降低,器件物理特性發(fā)生變化(如短溝道效應(yīng)加劇),這要求對邏輯門的模型和分析方法進(jìn)行持續(xù)更新。互連線延遲相對于門延遲的比重增加,使得邏輯門驅(qū)動長線時(shí)的性能分析更為復(fù)雜。

- 功耗管理技術(shù):基于對邏輯門功耗的深刻理解,設(shè)計(jì)者采用時(shí)鐘門控、電源門控、多閾值電壓技術(shù)等來有效控制動態(tài)和靜態(tài)功耗。

五、先進(jìn)邏輯門結(jié)構(gòu)

為了滿足高性能和低功耗的極端要求,標(biāo)準(zhǔn)CMOS邏輯門也在演進(jìn):

- 傳輸門邏輯:利用PMOS和NMOS并聯(lián)構(gòu)成雙向開關(guān),常用于構(gòu)建多路選擇器和鎖存器。

- 動態(tài)邏輯:通過預(yù)充電和求值階段,減少實(shí)現(xiàn)復(fù)雜邏輯所需的晶體管數(shù)量,從而獲得更高的速度,但需要時(shí)鐘控制且存在電荷泄漏等問題。

- 多米諾邏輯:是動態(tài)邏輯的一種改進(jìn),集成了靜態(tài)反相器,提高了噪聲容限和驅(qū)動能力。

結(jié)論

CMOS邏輯門電路分析是集成電路設(shè)計(jì)的核心基礎(chǔ)。它不僅是理解數(shù)字電路如何工作的鑰匙,更是進(jìn)行高性能、低功耗、高可靠性芯片設(shè)計(jì)的根本。從簡單的反相器到復(fù)雜的邏輯簇,對其靜態(tài)特性、動態(tài)響應(yīng)和功耗機(jī)理的精準(zhǔn)建模與仿真,貫穿于從架構(gòu)規(guī)劃、邏輯綜合到物理實(shí)現(xiàn)的整個(gè)IC設(shè)計(jì)流程。隨著工藝進(jìn)入納米尺度乃至更小,對CMOS邏輯門行為的深入分析,包括其非理想效應(yīng)和變異性的研究,將變得比以往任何時(shí)候都更加重要。

如若轉(zhuǎn)載,請注明出處:http://www.xaomwiu.cn/product/39.html

更新時(shí)間:2026-01-11 02:29:51