在當今數字化時代,企業官網、產品展示型網站和會員服務平臺已成為企業與客戶互動的重要橋梁。我們致力于提供專業的網站和小程序開發服務,并輔以可靠的托管支持,幫助客戶構建高效、美觀且功能完善的在線平臺。

企業官網型網站是企業的數字名片,不僅展示企業形象,還能傳達品牌價值。我們的開發團隊根據客戶需求,設計響應式布局,確保網站在各種設備上流暢運行,并優化SEO以提升搜索引擎排名。

產品展示型網站專注于突出產品特點和優勢。我們運用動態效果和交互設計,讓產品細節一目了然,同時集成購物車和支付功能,支持電商轉型,幫助企業快速吸引潛在客戶并促進銷售。

會員服務型網站和小程序旨在增強用戶粘性。我們開發會員管理系統,包含注冊、積分、優惠券等功能,提供個性化服務體驗。通過小程序的便捷性,用戶可以隨時隨地訪問服務,提升客戶忠誠度。

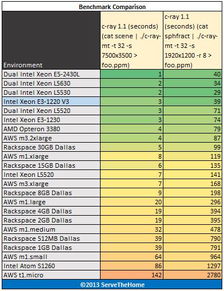

我們的網站托管服務確保平臺的穩定運行和安全防護。我們提供24/7監控、定期備份和技術支持,讓客戶專注于業務發展,無后顧之憂。

我們以專業的技術和貼心的服務,助力企業在數字世界中脫穎而出。無論是網站還是小程序開發,我們都力求創新與實用相結合,為客戶創造長期價值。