基于ISO/IEC 14443-A協議的無源電子標簽數字集成電路設計

隨著物聯網和智能識別技術的快速發展,基于ISO/IEC 14443-A協議的無源電子標簽在門禁系統、公共交通、電子支付等領域得到廣泛應用。無源電子標簽以其無需內置電源、體積小、成本低等優勢,成為射頻識別(RFID)技術中的關鍵組件。本文旨在探討基于14443-A協議的無源電子標簽數字集成電路設計的關鍵環節,包括協議分析、架構設計、模塊劃分以及優化策略。

理解14443-A協議是設計的基礎。該協議規定了讀寫器與標簽之間的通信頻率(13.56MHz)、調制方式(ASK 100%)、編碼方案(Miller編碼)以及數據幀結構。在數字集成電路設計中,必須確保標簽能夠正確解碼來自讀寫器的命令,并生成符合協議的響應信號。這包括實現協議中的防沖突機制、身份驗證流程以及數據交換協議,以確保標簽在多點環境下穩定工作。

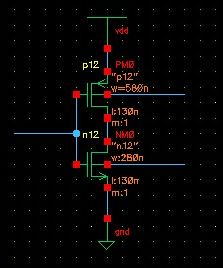

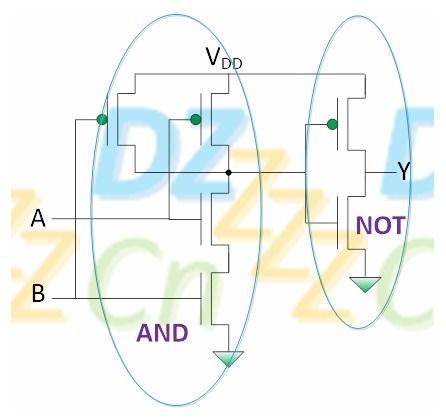

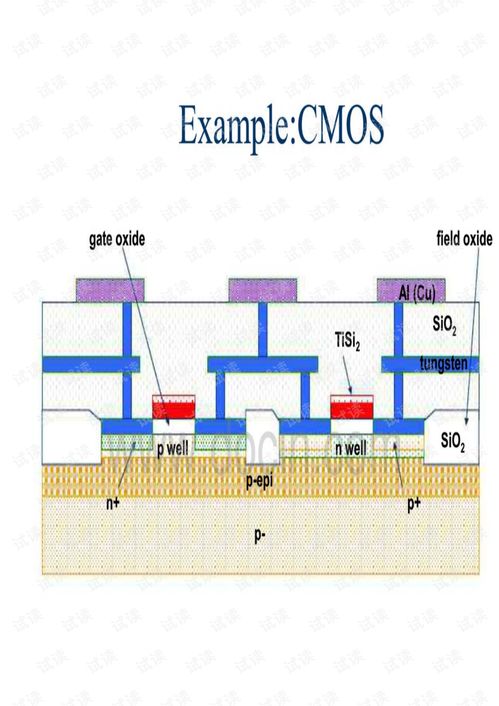

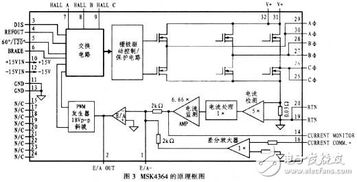

在架構設計階段,數字集成電路通常劃分為多個核心模塊:射頻前端接口、數字控制單元、存儲器和安全模塊。射頻前端接口負責從讀寫器的射頻場中獲取能量,并通過解調提取時鐘和數據信號;數字控制單元作為核心處理部件,執行協議狀態機、命令解析和數據管理;存儲器模塊用于存儲標簽的唯一標識符(UID)和用戶數據;安全模塊則實現加密算法,以保護數據傳輸的機密性和完整性。設計時需采用低功耗技術,如門控時鐘和電源門控,以最大化能量利用效率。

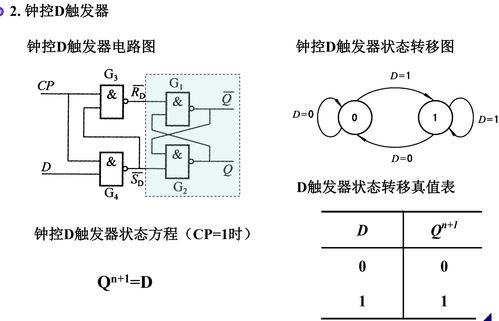

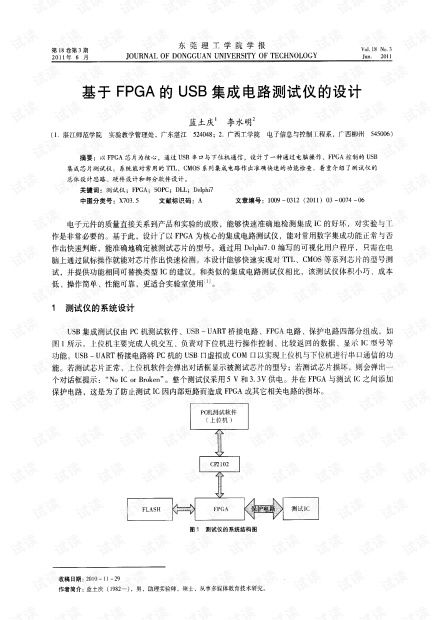

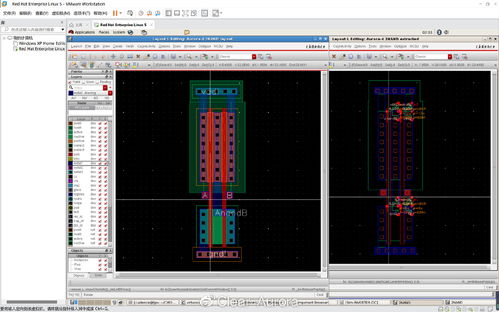

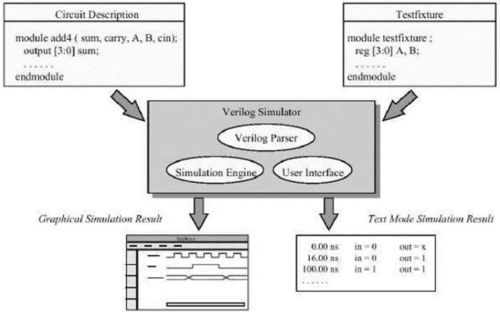

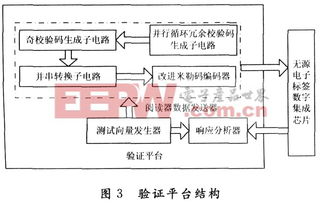

模塊劃分后,設計重點轉向電路實現和優化。例如,數字控制單元可采用有限狀態機(FSM)實現協議邏輯,確保快速響應讀寫器指令;存儲器模塊可能使用非易失性存儲器(如EEPROM)以保持數據持久性;安全模塊可集成輕量級加密算法(如AES或自定義流密碼)來滿足應用安全需求。在物理設計層面,需考慮布局布線、時序收斂和抗干擾能力,以應對高頻環境下的信號完整性挑戰。仿真和測試是關鍵步驟,通過軟件工具(如Cadence或Synopsys平臺)驗證設計是否符合協議規范和性能指標。

基于14443-A協議的無源電子標簽數字集成電路設計是一個多學科交叉的工程,涉及協議理解、架構規劃、電路實現和系統優化。通過精細化設計,可以實現高性能、低功耗和低成本的產品,推動RFID技術在更多場景中的應用。隨著半導體工藝的進步和協議演進,此類設計將向更高集成度和更強安全性方向發展。

如若轉載,請注明出處:http://www.xaomwiu.cn/product/16.html

更新時間:2026-01-11 22:51:42